Mr. Srinivasa Rao Kakumanu (KS)

Experience: 26+ Years

Educational Qualification: B.Tech from OU

KS was the CEO of the Institute of Silicon Systems. He has been in the VLSI industry for the last 26 years and he worked as General Manager, ASIC Design (India), Infotech Enterprises Ltd until the end of last year. Mr. KS led/managed 70+ ASICs all the way from 0.14um to 40nm – working at QualCore, TTM (and later Infotech – Infotech acquired TTM in Sept 2008), and Ikanos. He was in the US between 2000-2007, and managed teams at TTM inc., and Ikanos. Mr. KS quit Infotech in Nov 2010 and he has been training students at MosChip Academy of Silicon Systems & Technologies Private Limited (MAST) in Madhapur, Hyderabad since then.

Mrs. Sarala Beenedi

Experience: 32+ Years

Educational Qualification: M.Tech from JNTU

Miss. Sarala Beeneedi is the Technical Director of the Institute of Silicon Systems. She has over 32 years of industry experience spanning FPGA (Xilinx FPGAs) design, ASIC design, Digital Design, and Hardware design. She was in the USA from 2001 to 2005 and worked for a Physical Design services company (Time To Market Inc) as Senior ASIC Designer. She was Vice President of the FPGA group at Taray Technologies India Pvt Ltd and made a significant contribution to the growth of the company. She has extensive hands-on experience and played a key role for the last ten years being in a managerial position.

Mr. Anand Shankar Moghe

Experience: 35+ Years

Educational Qualification: Masters degree in ECE from the Philips International Institute in Netherlands

For the past few years Mr. Anand S Moghe was into training graduate engineers in VLSI so as to impart specific skills required to make them employable. He spent about 18 months working in a project under the DDUGKY scheme of Government of India, training graduate engineers who come with a rural background. A majority of these engineers are now employed with several reputed organizations across India.

Anand Moghe was a Senior Engineering Manager in Xilinx India at Hyderabad, at the time of his retirement from the industry in 2014. Prior to that he worked in senior management positions in companies like Cypress Semiconductors in Bangalore, and Mentor Graphics, Qualcore Logic and CMC – all in Hyderabad. He has also worked as Head of ASIC Design and Verification services in eInfochips, an Ahmedabad based company. Although his domain of experience has been microprocessor-based board level design and front-end VLSI digital design and IP (Intellectual Property) development, he has worked in an EDA tool company, semiconductor product companies and VLSI services organizations. He also had a stint in ECIL for 5 years, working in the area of RF transmitters and receivers for a defense project.

Anand Moghe was a visiting faculty at the Hyderabad campus of BITS, Pilani, where he taught Digital Signal Processing to M. Tech students. He has also delivered corporate training in Verilog at Semiconductor product companies like Sandisk and Maxim – both in Bangalore. He has lectured on DFT (Design for Testability) at VEDA IIT in Hyderabad for many years, and has also delivered technical lectures at conferences and seminars in India and abroad.

He obtained his Masters degree in Electronics and Communication Engineering from the Philips International Institute in Netherlands in 1983 and his Bachelors in (Electronics and Communication) Engineering from Osmania University in 1975.

Mr. Subbarao Y. K.

Experience: 15+ Years

Educational Qualification: M.Tech (Electronics-VLSI)

Mr. Subbarao currently working as a Senior Verification Engineer. He has been in the VLSI industry for 5+ years and teaching for 10+ years of experience. Expertise in Verification language, such as Verilog, System Verilog, and UVM. He is working as a verification engineer on various real-time projects.

Mr. Chandrarao Kondepati

Experience: 20+ Years

Educational Qualification: M.Tech (Electronics-VLSI)

Mr. Chandra Rao Kondepati is currently working as an senior analog layout manager in MosChip, leading a team of 50 members, and he has been working in the VLSI industry for the last 18 years. His expertise is in analog layout design for Power management circuits, PLL, DLL, Data Converter circuits, and SerDes. He has worked on multiple Test and Product chips all the way from 500nm to 5nm.

Prior to MosChip, He has been in the Analog Layout in different roles in various companies like Infotech, and Qualcore logic limited until 2011.

Mr. Thirupathi Kottapally

Experience: 20+ Years

Mr. Thirupathi Kottapally, Having 20+ years of proficient experience in the VLSI backend Analog Layout domain. Started career as an engineer and grown to a level of Senior Manager in Moschip Technologies. Expert in all Mixed signal circuits like Serdes, DDR’s, PMU(power management unit, Data Converters, Transceivers and Clocking circuits like Oscillators, PLL and DLL etc. Experience in latest challenging technical nodes from1.8nm to 180nm.

Passionate to train and mentor engineers to professional Analog Mask designers. Having good technical excellence and expertise, trained close to 700+ engineers and they reached to great heights in their career.

Proficiency in development of Academic training material, covers all concepts of electronics, Guidelines of Mask design, Issue tracer and debugging skills etc. Special focus on programming languages like C-shell, Perl and Skill languages.

Expertise in Friendly teaching encourages the students to participate in the classroom discussions to exchange the ideas and thoughts.

Mr. Chandrasekhar Kanireddy

Experience: 20+ Years

Educational Qualification: B.Tech

Mr. Chandrasekhar Kanireddy, having 20+ years of hands-on experience in Analog and Mixed-Signal Layout design. Started career as an engineer and grown to a level of Senior Manager in MosChip Technologies Ltd. Had tape out experience of 50+ ASICs of different complexities, by leading & managing the mixed signal layout design teams. Expertise in project management, people management and ASIC design flow development. Expertise in Transceiver layout designs such as SerDes and DDRs, Clocking circuits like PLL, DLL and Oscillators, Data converters like ADC and DAC, PMUs, and IO layouts in latest challenging technology nodes from 3nm to 180nm across major silicon foundries.

Enthusiastic to train and mentoring the engineers to professional Analog Mask designers. Having good technical excellence and expertise, trained close to 700+ engineers and they reached to great heights in their career. Proficiency in development of Academic training material, covering all concepts of electronics, Guidelines of Mask design, Issue tracer and debugging skills etc. Special focus on programming languages like C-shell, Perl and Skill languages. Expertise in Friendly teaching encourages the students to participate in the classroom discussions to exchange their ideas and thoughts.

Dr. Nagadeepa Choppakatla

Experience: 16+ Years

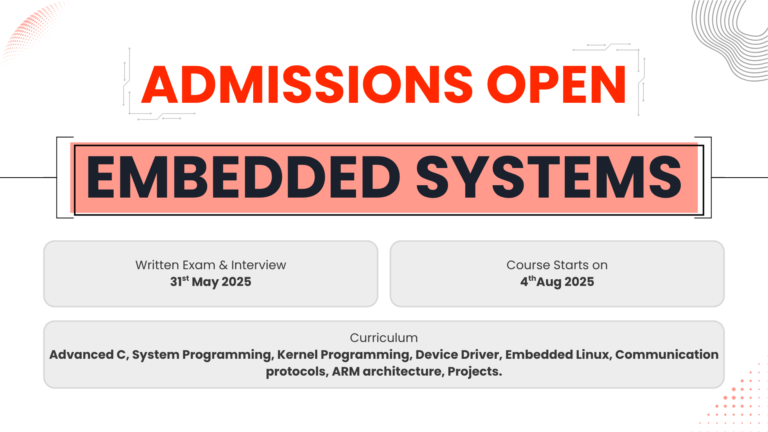

Educational Qualification: Ph.D. in Embedded-Artificial Intelligence Systems

Dr. Nagadeepa Choppakatla is currently working as corporate trainer for Embedded Software.

She did Ph.D. in Embedded-Artificial Intelligence Systems, M. Tech. in Embedded Systems, and B. Tech. in ECE from JNTU, Hyderabad.

She has 12+ years of experience as academician & researcher and had 3.5 years of experience as System Design Engineer for an electronic industry. She has around 20 International publications in various Journals and Conferences. Her expertise is in Artificial Intelligence and Embedded System Design. She was involved in projects like driver assistance system, vehicle tracking and speed warning system, IoT based controlled assistance system using hand gestures, etc.

Mr. Kishore Vennela

Experience: 12+ Years

Educational Qualification: Ph.D. in VLSI Architectures for Robot Control Systems (Pur)

Mr. Kishore Vennela holding a M.Tech Degree from JNTU, Hyderabad and pursuing Ph.D in the domain of VLSI Architectures for Robot Control Systems. He has 12+ years of teaching experience and published research articles on Indoor Robot Application with optimum sensing system. He has good experience in hardware level developments on Zynq-7 and Artix-7 series FPGA’s. He is currently working as Corporate trainer for Design Verification in the MAST. His area of interest includes Automated Robotic Systems, Optimum VLSI Architectures, and Realtime Verification of FPGA Design Models.

Mr. Sarath Chandra Karanam

Experience: 13+ Years

Educational Qualification: Ph.D. in VLSI ON LOW POWER SRAM DESIGN.

Dr. K. Sarath Chandra Karanam is currently working as a corporate trainer – Analog layout. He did his Ph.D. in the VLSI domain on LOW POWER SRAM DESIGN, M. Tech. in VLSI from VIT University, Vellore, and B. Tech. in ECE from JNTU, Hyderabad.

He has 11+ years of experience as an academician & researcher. He has around 10 international publications in various reputed journals and conferences. His expertise is in Analog IC Design, Analog Layout, and Low Power VLSI Design. He was involved in projects like SERDES.

Mr. Naresh Kattekola

Experience: 13+ Years

Educational Qualification: Ph.D. from NIT Meghalaya in Low Power VLSI and Image Processing

Dr. Naresh Kattekola is currently working as a Corporate Trainer in Physical Design, specializing in floor planning, placement, clock tree synthesis, routing, and timing closure, utilizing industry-standard EDA tools such as Cadence Innovus and Genus. With extensive expertise in ASIC design and VLSI methodologies, he has been instrumental in training engineers and optimizing semiconductor design processes. Previously, he served as an Assistant Professor at VNR VJIET, guiding M.Tech students in approximate computing, low-power VLSI, and FPGA-based designs, contributing to over 13 research publications in reputed IEEE and Scopus-indexed journals. Additionally, he has authored a book chapter in CRC Press on VLSI and Hardware Implementations using Machine Learning, focusing on Approximate Computing and CNN for microwave imaging applications. With a proven track record in academia and industry, Dr. Naresh is committed to bridging the gap between theoretical learning and practical VLSI industry applications, shaping the next generation of semiconductor engineers through advanced training and research-driven education.